Цифровая обработка сигнала в гидролокаторах. Современные решения

Использование методов цифровой обработки сигнала (ЦОС) в гидролокаторах началось в конце 1950-х годов. Функции обработки сигнала ранних вариантов были довольно примитивными, и достигаемые результаты ограничивались существующей технологией, которая не обеспечивала удовлетворительное хранение данных и быстродействие процессоров. В начале 1970-х годов появились микросхемы ОЗУ, ПЗУ, АЛУ и микропроцессоров. Эти приборы легли в основу программируемых устройств обработки сигнала. А с появлением в начале 1980-х годов разнообразных БИС, быстродействующих арифметических процессоров, однокристальных микрокомпьютеров и ОЗУ большой емкости оказалось возможным создавать как системы с достаточно высоким быстродействием, так и малогабаритные адаптивные системы реального времени. После разработки и выпуска фирмой IBM в 1981 году персонального компьютера последовали внушительные инвестиции в развитие микросхем памяти и микропроцессоров. В результате кремниевая технология получила быстрое развитие, и в начале этого столетия многие полупроводниковые заводы уже смогли выпускать микросхемы с субмикронными топологическими нормами. На этом этапе ряд компаний приступили к поставкам процессоров цифровой обработки сигнала (DSP) с минимальными размерами элементов 250–130 нм, содержащих программируемые ПЗУ, ОЗУ для хранения данных и 24- или 32-разрядные АЛУ. Их быстродействие составляло несколько сот миллионов арифметических операций в секунду. Такие приборы, как правило, предназначались для построения однопроцессорных систем, и их архитектура была оптимизирована для выполнения функций фильтров с конечной импульсной характеристикой (КИХ) или быстрых преобразований Фурье (БПФ) в реальном времени.

Разработка специализированных микросхем (ASIC) с уровнем интеграции до 108 вентилей на кристалле привела к возможности создания необходимых для гидролокаторов систем на кристалле, СнК (System on Chip, SoC). Правда, дальнейшее масштабирование размеров элементов микросхем уже не приводит к существенному улучшению их производительности, что связано с ростом потребляемой мощности. Для решения этой проблемы крупные предприятия-производители микросхем прибегают к экзотическим технологиям, таким как применение напряженного кремния или затворных диэлектриков с высокой диэлектрической постоянной (high-k dielectrics). Но высокие стоимость САПР и расходы на переоснащение производства для выпуска таких микросхем привели к тому, что доступ малых системных компаний к этим технологиям оказался затруднен. Они уже не могут производить ASIC для цифровой обработки сигнала с использованием передовых технологических процессов. Таким образом, достаточно большие сроки проектирования, не возмещаемые расходы на проектирование и внедрение в производство, неспособность модифицировать микросхемы в случае необходимости изменения их алгоритма привели к отказу от применения ASIC для цифровой обработки сигнала.

Была сделана попытка решения проблемы цифровой обработки сигнала с помощью печатных плат с секционированной архитектурой, используя, например, быстродействующие ОЗУ и различные умножители или умножители/накапливающие сумматоры. Однако с увеличением сложности схем эти довольно простые базовые блоки ЦОС отстали от передового уровня. На выручку пришли FPGA, которые благодаря высоким плотности размещения элементов и быстродействию могут выполнять большое число функций обработки сигнала [1].

Устройства постобработки/отображения данных матрицы датчиков, входящие в рабочую станцию гидролокатора, должны выполнять следующие функции:

преобразование сигнала и дискретизацию аналоговых гидроакустических данных;

запись гидроакустических данных с помощью цифрового регистратора или массива независимых жестких дисков;

формирование действительного или отображаемого сигнала;

фильтрацию/демодуляцию/корреляцию опорного сигнала;

вывод аналогового сигнала для мониторинга.

Выходные отфильтрованные и/или демодулированные сигналы, или результаты корреляции опорного сигнала обычно поступают в приемную систему обработки сигнала гидролокатора для выполнения БПФ и воспроизведения изображения (рис.1). Такая система должна иметь большое число согласованных по усилению и фазе каналов, большой динамический диапазон, сложные интерфейсы и средства форматирования данных. Ее вычислительные ресурсы должны быть достаточными для формирования, фильтрации и демодуляции сигнала. Кроме того, она должна обеспечивать высокую скорость передачи данных [2]. Для экономически эффективного решения этих многочисленных проблем обработки гидроакустических сигналов компания Interactive Circuits and Systems для каждого функционального модуля устройства постобработки/отображения данных (см. рис.1) разработала набор архитектур плат стандарта VMEbus. Благодаря уникальной потоковой архитектуре эти модули могут быть быстро интегрированы для создания любой гидролокационной системы [2].

Основные функции обработки сигналов

В общем случае по основным функциям цифровой обработки сигнала гидролокатор подобен радарам и телекоммуникационным системам. К ним относятся такие функции, как:

преобразование сигнала: БПФ, различные теоретические преобразования, преобразования Хафа, Адамара и др.;

фильтрация: корреляция/свертка, функции получения КИХ/БИХ, интерполяция/прореживание, медианная фильтрация, функции фильтра Калмана, адаптивные линейные измерения и др.;

матричная алгебра: матричное умножение/инверсия/ротация, одновременная передача голоса и данных, нахождение собственных значений/собственных векторов матрицы и др.;

преобразование данных (отображение в полутоновой шкале и др.), сортировка и др.

Однако по методам реализации функций обработки сигнала системы гидролокатора часто сильно отличаются от систем других комплексов. Так, необходимость поиска по широкому полю и обеспечения при этом высоких показателей обнаружения и локализации цели требует применения больших сенсорных матриц и многоканальной обработки данных [1]. Для повышения вероятности обнаружения в конкретных условиях разнообразных целей, отличающихся по своим характеристикам, ряд операций обработки одного набора данных часто выполняются одновременно. Поэтому по производительности системы гидролокатора не должны уступать другим цифровым системам, а в ряде случаев и превосходить их.

Каковы достоинства применения микросхем FPGA в системах гидролокаторов?

Реализация функций ЦОС в микросхеме FPGA – трудоемкая задача, однако при этом конструкторам предоставляются значительные возможности повышения быстродействия и гибкости в реализации системы. Главные причины, стимулирующие интегрирование функций цифровой обработки сигнала в FPGA, – уменьшение массогабаритных показателей и мощности на системном уровне. Так, несмотря на неблагоприятное соотношение между потребляемой мощностью и полосой пропускания цифрового сигнала, применение FPGA позволяет сократить потребляемую мощность системы благодаря возможности выбора напряжения ядра или за счет анализа напряжения критических линий связи. К тому же устранение линий передачи данных между отдельными FPGA и сигнальными процессорами приводит к значительному снижению потребляемой мощности и, следовательно, уменьшает нагрев системы. Это в свою очередь облегчает проблемы охлаждения конструкции. Современные программы проектирования, размещения и трассировки также позволяют существенно сократить энергопотребление схемы FPGA. В ряде случаев даже очень сложные и адаптивные операции цифровой обработки сигнала приемного блока радио- или гидролокатора могут эффективно выполняться встроенным процессором на базе FPGA. При необходимости проведения операций с плавающей запятой процессоры на основе FPGA обеспечивают большую гибкость, если конструкторы системы прибегают к строгому проектированию ее архитектуры. Поставщики FPGA предлагают конструкторам в качестве интеллектуальной собственности эффективные и точные операторы с плавающей запятой, инструментальные средства для выплнения БПФ и компиляторы фильтров [3].

Применение FPGA для цифровой обработки сигналов гидролокатора обеспечивает его превосходство по производительности перед локатором на традиционных устройствах обработки сигнала. В приложениях, для которых производительность является основным требованием (например, параллельное выполнение математических операций с плавающей запятой), можно поступиться эффективностью обработки ради получения высокого быстродействия. Вместе с тем, если допускается средняя производительность, но применение логических элементов ограничено, FPGA с высоким уровнем итерации может достаточно эффективно выполнять математические расчеты. Таким образом, проектировщик получает возможность выбора между быстродействием и числом логических элементов, требуемых для каждой операции цифровой обработки сигнала. К тому же, возможность выполнения цифровой обработки сигнала микросхемой FPGA облегчает внесение изменений в спроектированную систему.

Существующие инструментальные средства перевода алгоритмов процессора с языка Си на аппаратный язык, например VHDL, могут быть использованы для реализации отдельных логических функций стандартного процессора сопроцессором FPGA, работающим параллельно с основным процессором, или для переноса всех операций основного процессора в FPGA. Это обеспечивает дополнительную гибкость при конструировании архитектуры гидролокаторов.

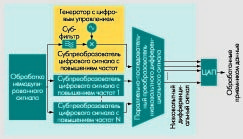

Чем больше ресурсов у микросхемы FPGA, тем шире конструктор может использовать полифазную фильтрацию и преобразование с понижением частоты (рис.2). Многочисленные встроенные в сложную микросхему FPGA внешние генераторы с цифровым управлением могут обеспечить высококачественную фазовую дискриминацию.

Возможна поставка или разработка по заказу опытных образцов микросхем FPGA с оптимизированными характеристиками для выполнения операций матричной инверсии.

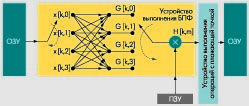

При разработке опытного образца и масштабировании системы весьма полезна возможность выполнения микросхемой FPGA быстрых преобразований Фурье (рис.3). Однако, фактически главное достоинство FPGA с точки зрения выполнения БПФ – способность выбора оптимального баланса между быстродействием системы и числом элементов, требуемых для параллельной реализации сложных БПФ. А исполнение сложных БПФ является одной из важнейших функций любой системы, и достоинства FPGA здесь очевидны.

Поскольку конструкторы радиолокаторов, гидролокаторов и телекоммуникационных систем фокусируют свое внимание на выполнение сложных операций формирования многоэлементного луча и генерации формы сигнала, поставщики программируемых логических схем располагают собственными инструментальными средствами и генераторами для проведения больших, сложных преобразований. Сюда относятся опытные разработки и IP-ядра для стандартных и нестандартных конструкций, а также БПФ-сопроцессоры, которые оказывают существенную поддержку программируемой логике [3].

Перспективно применение FPGA и в гидролокационных системах с синтезированной апертурой (Synthesized Aperture Sonar, SAS), которые представляют собой один из самых точных на сегодняшний день акустических датчиков движения и находят все более широкое применение как в военных системах (для обнаружения и классификации мин), так и системах промышленного назначения (для газо- и нефтедобычи на шельфе).

Для формирования высококачественного SAS-изображения необходимо точно определять изменение формы синтезированной апертуры в результате нежелательных перемещений локатора. Для решения этой задачи в общем случае используются акустические методы оценки движения, или так называемая техника микронавигации. При этом для получения сопоставимых значений разрешения при определении дальности и азимута цели используются широкополосные согласованно фильтрованные гидролокационные импульсы. Функции согласованной фильтрации, микронавигации и формирования сигнала гидролокатора могут выполнять как DSP, так и FPGA.

Но универсальные микросхемы DSP и FPGA совершенно разные "существа" со своими достоинствами и недостатками. Как правило, FPGA целесообразно применять, когда нужны высокая скорость обработки данных, параллелизм работы, эффективность и гибкость ввода-вывода. Кроме того, FPGA дешевле DSP, имеют меньшие габариты и потребляют меньшую мощность. При интеграции в систему гидролокатора с критичными требованиями к занимаемой площади и мощности FPGA может заменить 10 одноплатных процессоров, выполняющих отдельные функции системы [4]. Достоинства DSP – возможность выполнения операций с плавающей запятой и повторного использования кода, а также простота разработки. Другими словами, при решении прямых, хорошо поставленных задач высокоскоростной обработки сигнала лучшие результаты можно получить с помощью FPGA, тогда как DSP позволяют реализовывать сложные алгоритмы и операции с плавающей запятой.

В большинстве систем цифровой обработки сигнала необходимо применять компоненты и с теми, и с другими свойствами. Вот почему вместо развертывания конкуренции между этими двумя типами устройств цифровой обработки сигнала гораздо полезнее совместно использовать их достоинства, смягчая недостатки, и создавать гибридные архитектуры. Конечно, получить эффективную гибридную архитектуру гораздо сложнее, чем просто соединять FPGA с сигнальным процессором, поскольку необходимо решить такие задачи, как обеспечение интерфейса ввода-вывода, интерфейса хоста, соединений процессоров, определения конфигурации памяти, средств управления. Не говоря уже о структуре FPGA и разработке программного обеспечения, благодаря которому система становится доступной пользователю. Тем не менее, большинство архитектур современных устройств обработки сигналов в реальном времени содержат и FPGA, и DSP. К выпуску платформ такого типа приступили многие компании, в том числе Cray и Spectrum Signal Processing [5].

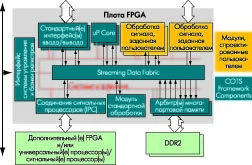

Пример такой системы – гибридная платформа GT-6U-VME (GTV6), выполненная на специализированной VME-плате типоразмера 6U компании Bittware [6] – ведущего поставщика на рынке аппаратных средств обработки сигнала военного/аэрокосмического и промышленного назначения, выполненных на базе готовых к применению коммерческих устройств, IP-систем и системных решений. В систему входят две FPGA семейства Stratix II GZ (2SGX90 и 130) компании Altera, кластер, содержащий два сигнальных процессора семейства TigerSHARC (ADSP-S201S) компании Analog Devices, и DDR2 синхронное ДОЗУ емкостью до 3 Гбайт. Конструкция охлаждаемой за счет теплопроводности платы оптимизирована и пригодна для применения в современных системах многопроцессорной обработки данных и в будущем оборудовании военного назначения. Интеграция FPGA и сигнального процессора реализуется с помощью базового средства проектирования ATLANTiS FrameWork компании Bittware, которое предусмотрено в каждой микросхеме FPGA семейства Stratix II GZ и позволяет распределять ресурсы ввода-вывода по всем или одному процессору, а также выполнять маршрутизацию всех данных на плате и вне ее (рис.4). Двойное средство ATLANTiS обеспечивает пропускную способность канала 5 Гбайт/с, оставляя FPGA достаточно ресурсов для дополнительной обработки данных.

Основной компонент платформы GTV6 – программируемые пользователем вентильные матрицы, каждая из которых содержит 132540 эквивалентных логических элементов, ОЗУ емкостью 6,7 Мбит, 252 встроенных умножителя 18×18, 63 блока цифровой обработки сигнала и восемь блоков ФАПЧ. Каждая программируемая вентильная матрица выполняет пред-, пост- и совместную обработку и входит в один из кластеров на основе сигнальных процессоров. При этом скорость бесперебойной передачи данных с помощью ATLANTiS составляет 2 Гбайт/с.

Частота сигнального процессора S201S составляет 600 МГц, производительность – 3,6 Gflops, при работе с плавающей запятой – 14,4·106 операций/с. В микросхему сигнального процессора входят ОЗУ емкостью 24 МГц, четыре быстродействующих дуплексных LVDS линк-порта, обслуживающих четыре выходных и четыре входных канала со скоростью передачи данных в каждом направлении 500 Мбайт/с. Два линк-порта каждого сигнального процессора предназначены для формирования кольца межсоединений процессоров, оставшиеся два – для передачи данных через ATLANTiS. Платформа средств цифровой обработки сигналов SAS-гидролокатора компании Bittware последнего поколения уже содержит два кластера, в каждый из которых входят по четыре сигнальных процессора семейства TigerSHARC компании Analog Devices, и DDR2 синхронное ДОЗУ емкостью 8 Гбайт.

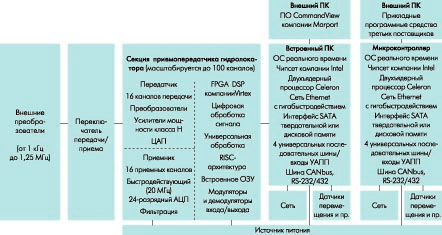

Многие гидролокационные системы устаревают и не могут поддерживать изменения, необходимые для выполнения новых задач. Решения проблемы старения обычно предусматривают замену, а не модификацию существующих систем, что является дорогостоящим мероприятием. Чтобы снизить риск и затраты на создание средств обнаружения и связи следующего поколения, компания Marport C-Tech разработала и сконструировала программируемый гидролокатор [7]. Он представляет собой высокопроизводительный приемопередатчик с быстрой перестройкой частоты в диапазоне от 1 кГц до 1,25 МГц и малыми габаритами (рис.5). В отличие от конструкций на основе аппаратных средств, выполняющих фиксированные функции, архитектуру электронных систем программируемого гидролокатора можно динамически реконфигурировать для выполнения различных режимов локатора. Большая часть функций обработки акустического сигнала выполняется программируемыми, а не специализированными аппаратными средствами.

Электронная система программируемого гидролокатора выполнена на основе приемопередающих модулей, названных "секциями" гидролокатора (sonar blades). Каждый модуль имеет 16 передающих и 16 приемных каналов. Их число может быть увеличено до нескольких сотен, с тем чтобы поддерживать работу с разнообразными многоэлементными преобразователями. Размер базового модуля составляет 12×12×16 см, размер дополнительного модуля – 12×12×5 см. Многочисленные секции электронной системы могут работать синхронно, поддерживая до 2048 каналов приема-передачи. Разработанные алгоритмы цифровой обработки сигнала поддерживают многорежимную работу гидролокатора, а также связь с коммерческими системами навигации (такими, как GPS) и сенсорами движения и определения углового пространственного положения судов. Все данные гидролокатора могут передаваться системам геопространственной информации или центрам управления боевыми действиями, в том числе и подводным.

В модуль входит FPGA семейства Virtex 5 компании Xilinx, высокопроизводительные блоки цифровой обработки сигнала которого выполняют функции фильтрации, БПФ, корреляции, модуляции широкополосного сигнала и др. FPGA может эмулировать 32-разрядный микропроцессор, способный работать с программно-аппаратными средствами любого типа. Обработанные данные передаются встроенному процессору для выполнения математических расчетов.

Кроме того, модуль содержит генератор сигнала, интегрированный с процессором, работающим с ОС реального времени Lunix и со встроенными 24-разрядными АЦП с частотой дискретизации 20 МГц, позволяющими выполнять сбор и обработку данных в реальном времени. Число каналов, обслуживаемых АЦП, достигает 2048.

Связь между процессором и FPGA осуществляется в соответствии со стандартом, разработанным компанией Marport и обеспечивающим ввод-вывод данных по протоколу управления передачей/межсетевому протоколу (TCP/IP). Интерфейс поддерживает высокую скорость передачи данных между аналоговыми входами, элементами цифровой обработки и аналоговыми выходами. Стандарт позволяет многочисленным интерфейсам совместно использовать один кабель и осуществлять синхронную передачу данных между многочисленными каналами системы сбора данных и элементами обработки сигнала. Предусмотрена возможность передачи данных датчиков сторонних поставщиков через GigaEthernet или USB. В конструкцию входит встроенный запасной процессор для связи с такими внешними устройствами, как система управления боевыми задачами (рис.6) [7].

Модульная конструкция позволяет значительно уменьшить массогабаритные показатели, потребляемую мощность и стоимость электроники как существующих, так и будущих платформ гидролокаторров.

Отечественное аппаратное решение для цифровой обработки сигналов гидролокаторов – гетерогенные многоядерные системы на кристалле серии "Мультикор"

Сегодня в России, как и во всем мире, подходы к созданию электронных устройств и систем, работающих в тяжелых условиях эксплуатации, существенно изменились. Основная тенденция – переориентация на специализированные изделия с сокращенным циклом проектирования и производства, что позволяет достигать максимальной эффективности при выполнении конкретных задач управления, контроля, сбора и обработки информации. На передний план выходит концепция построения системы на кристалле, появившаяся в 1990-е годы. Такие микросхемы представляют собой эффективные средства построения многих классов телекоммуникационной, гидролокационной и радиоэлектронной аппаратуры. Можно выделить три характерные особенности системы на кристалле:

наличие функционально законченного набора модулей управления и обработки данных;

использование IP-блоков в качестве основных структурных элементов;

наличие встраиваемых программируемых процессорных ядер.

В системе на кристалле интегрированы функции, для исполнения которых обычно требуется набор микросхем. Это, с одной стороны, позволяет существенно увеличить пропускную способность соединений компонентов на кристалле по сравнению с пропускной способностью линий связи различных кристаллов, реализующих каждый отдельную функцию. И, как следствие, поднять производительность систем. С другой стороны, при уменьшении числа кристаллов резко упрощается изготовление и монтаж плат, что ведет к повышению надежности и снижению стоимости системы. В СнК интегрированы интерфейсы сетевых и телекоммуникационных систем, благодаря чему можно без дополнительных адаптеров соединять микропроцессоры друг с другом, с телекоммуникационными и вычислительными сетями. Применение в качестве IP-блоков полнофункциональных DSP-ядер позволяет использовать СнК для выполнения алгоритмов поточной высокоскоростной обработки, а наличие универсальных вычислительных ядер – реализовывать функции управления и несистематических алгоритмов, что значительно упрощает проектирование систем.

В настоящее время существует перспективная элементная база двух типов, на основе которой может быть построена система цифровой обработки сигнала гидролокатора (рис.7). Первое аппаратное решение основывается на сочетании FPGA, или программируемой цифровой обработки сигнала (ПЦОС), и универсальных процессоров с RISC-подобной архитектурой. Второе – это многоядерные гетерогенные СнК, объединяющие универсальные RISC-подобные и специализированные процессорные ядра для цифровой обработки сигналов.

Гетерогенные СнК серии "Мультикор", разрабатываемые в ГУП НПЦ "ЭЛВИС", на сегодняшний день являются передовой отечественной элементной базой и применимы в качестве аппаратного решения задач гидролокации. Сочетание двух типов ядер (RISC и DSP) позволяет создавать сложные системы и достигать высокой производительности при сигнальной (первичной) обработке и алгоритмах вторичной обработки. Для этой серии СнК характерен высокий уровень параллелизма на уровне процессорных ядер, инструкций и операций.

Немаловажное значение при реализации гидролокационных комплексов имеет наличие периферийных быстродействующих устройств (табл.1). Аппаратная поддержка Ethernet способствует проектированию гидролокаторов как IP-устройств, функционирующих в локальной сети, объединяющей датчики охранных систем в один комплекс. Порт видеоданных (VPOUT) позволяет выводить яркостную карту зоны обзора напрямую в видеопамять и, соответственно, на экран монитора, то есть наличие в СнК видеопорта позволяет создавать полностью встраиваемую систему без использования ПК.

Алгоритмическая база СнК серии "Мультикор" содержит большое число библиотек и встроенных функций (библиотеки элементарных функций, спектрального анализа, адаптивной фильтрации) [8], что обеспечивает быструю разработку высокоскоростных систем цифровой обработки. Система инструкций и высокий уровень параллелизма, характерный для новых процессоров серии "Мультикор", определяют число одновременно выполняемых арифметических операций умножения/сложения/вычитания. Сравнение СнК с современными системами цифровой обработки радиолокационных сигналов SAS-гидролокатора были рассмотрены для следующих параметров сигнала и представления данных:

Длина импульса Р…………………………………….1536 выборок

Длина импульса БПФ N…………………………....4096 слов или выборок

Частота широкополосной выборки…………….75 кГц

Представление данных……………………………32 бита на выборку

(16 реальных, 16 мнимых)

На основе предоставленных данных и алгоритма обработки на примере SAS рассчитаны характеристики сигнальной обработки (табл.2).

Характеристики сигнальной обработки на СнК NVCom-01 и MCom-02 показали, что отечественные СнК серии "Мультикор" могут быть применены в качестве аппаратной платформы для реализации алгоритмов первичной обработки. Однако построение такой системы с характеристиками, аналогичными типовым функциям гидролокатора цифровой обработки сигнала на основе FPGA XC4VX35, возможно при объединении шести-восьми СнК модели MCom-2 в распределенную систему обработки.

Таким образом, отечественное аппаратное решение задачи цифровой обработки сигналов гидролокаторов на основе гетерогенных многоядерных систем на кристалле серии "Мультикор" полностью соответствует современным требованиям сигнальной обработки и может быть применено как в пассивных, так и в активных гидролокаторах.

Литература

1. Curtis T. Sonar Technology – past and current.– Curtis Technology (UK) Ltd, 2004.

2. Roy D. Rapid deployment of sonar processing systems. –Interactive Circuits and Systems Ltd.

3. Kenny R. FPGA signal processing for radar/sonar applications.– www.mobiledevdesign.com/hardware_news/fpga-signal-processing-sonar-dsp-1207

4. Banks S. et al. FPGA based real time synthetic aperture sonar processing for AUVs. – Proceedings of the Institute of Acoustics, 2006, v.28, Pt.5.

5. McHale J. FPGAs enhance military signal-processing applications. www.militaryaerospace.com/index/display/article-display/275875/articles/military-aerospace-electronics/volume-17/issue-10/features/technology-focus/fpgas-enhance-military-signal-processing-applications.html

6. www.bittware.com/applications/Ap-stories/sonar.cfm

7. Software Defined Sonar. www.marport.com/defence/technology/software-defined-sonar

8. www.multicore.ru

eng

eng